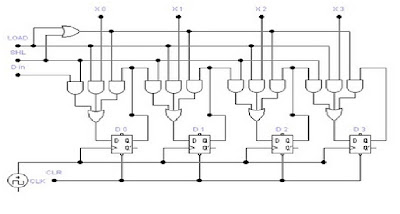

REGISTER GESER TERKENDALI

1. Gambar Rangkaian

2. Prinsip Kerja

Kendali SHL

SHL merupakan sinyal kendali. Apabila SHL rendah, maka sinyal SHL tinggi. Keadaan ini membuat setiap keluaran flip-flop masuk kembali ke masukkan data-datanya. Karena itu, data tetap tersimpan pada setiap flip-flop pada saat pulsa detak tiba. Dengan cara ini, sebuah kata digital dapat tersimpan selama waktu yang diinginkan.

Sebuah register geser terkendali (controlled shift register) mempunyai masukan - masukan kendali, yang mengatur operasi rangkaian pada pulsa pandetak yang berikutnya.

Pengisian Peralel

Gambar diatas menunjukkan langkah yang lain dalam evolusi register-register geser. Rangkaian ini dapat megisikan semua bit X secara langsung ke dalam flip-flop, sama seperti register buffer. Cara pemasukan data seperti ini disebut pengisian paralel atau serentak (parallel or broadside loading). Dan untuk data yang banyak hanya dibutuhkan satu pulsa pendetakan untuk menyimpan data - data tersebut.

Jika LOAD dan SHL rendah, keluaran gerbang NOR akan menjadi dan keluaran flip-flop akan mengumpan kembali ke masukan datanya. Keadaan ini menyebabkan data tetap tersimpan dalam masing-masing flip-flop positif dari pulsa detik. Dengan kata lain, register menjadi tidak aktif ketika LOAD dan SHL dalam keadaan rendah dan isi register tersimpan dengan aman.

Apabila LOAD rendah dan SHL tinggi, rangkain bertindak sebagai register geser-kiri. Dipihak lain, jika LOAD tinggi dan SHL rendah, rangkaian berfungsi sebagai register buffer karena semua bit X akan memasuki flip-flop untuk pengisian Paralel. (LOAD dan SHL tidak boleh tinggi bersam-sama, karena 2 ragam operasi yang berbeda tidak mungkin dilaksanakan dengan sinyal detak tunggal).

Dengan menambahkan banyak flip-flop, kita dapat membuat register geser yang lebih panjang. Dan dengan gerbang yang lebih banyak, operasi pergeseran kek kanan dapat pula dilaksanakan. Sebagai contoh, 74198 adalah register 2 arah 8-bit jenis TTL, yang dapat melakukan pengsian secara serentak, penggeseran ke kiri atau penggeseran ke kanan.

.jpg)